# 1/2.3-Inch 14 Mp CMOS Digital Image Sensor

# MT9F002 Data Sheet, Rev. H

For the latest data sheet, please visit: www.onsemi.com

# Features

- 1.4 μm pixel with ON Semiconductor A-Pix<sup>™</sup> technology

- Simple two-wire serial interface

- Auto black level calibration

- Full HD support at 60 fps for maximum video performance

- 20 percent extra image array area in full HD to enable electronic image stabilization (EIS).

- Support for external mechanical shutter

- Support for external LED or xenon flash

- High frame rate preview mode with arbitrary downsize scaling from maximum resolution

- Programmable controls: gain, horizontal and vertical blanking, frame size/rate, exposure, left–right and top–bottom image reversal, window size, and panning

- Data interfaces: parallel or four-lane serial highspeed pixel interface (HiSPi™) differential signaling (SLVS)

- On-chip phase-locked loop (PLL) oscillator

- Bayer pattern downsize scaler

# **Applications**

- Digital video cameras

- Digital still cameras

# **General Description**

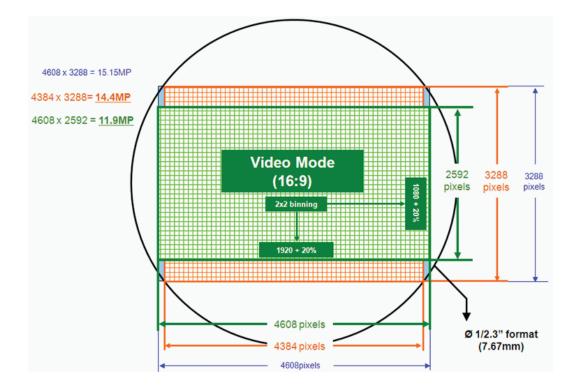

The ON Semiconductor MT9F002 is a 1/2.3-inch CMOS active-pixel digital imaging sensor with an active pixel array of 4608H x 3288V (4640H x 3320V including border pixels). It can support 14-megapixel (4384H x 3288V) digital still images and a 1080p plus additional 20 percent pixels for electronic image stabilization (4608H x 2592V) in digital video mode. The MT9F002 sensor is programmable through a simple two-wire serial interface, and has low power consumption.

#### Table 1: Key Performance Parameters

| Parameter                      |                                                            | Value                                                                                                                                                                                                                                   |  |

|--------------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

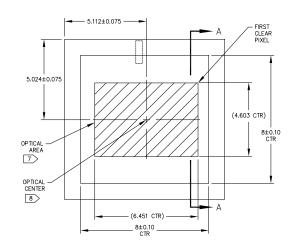

| Optical format                 |                                                            | 1/2.3-inch (4:3)                                                                                                                                                                                                                        |  |

| Active pixels and imager size  |                                                            | <ul> <li>4608H x 3288V: (entire array): 6.451mm (H)<br/>x 4.603mm (V), 7.925mm diagonal</li> <li>4384H x 3288V (4:3, still mode): 6.138mm<br/>(H) x 4.603mm (V), 7.672mm diagonal</li> <li>4608H x 2592V (16:9, video mode):</li> </ul> |  |

| Active pla                     | keis und indger size                                       | 6.451mm (H) x 3.629mm (V), 7.402mm diagonal                                                                                                                                                                                             |  |

| Pixel size                     |                                                            | 1.4 μm x 1.4μm                                                                                                                                                                                                                          |  |

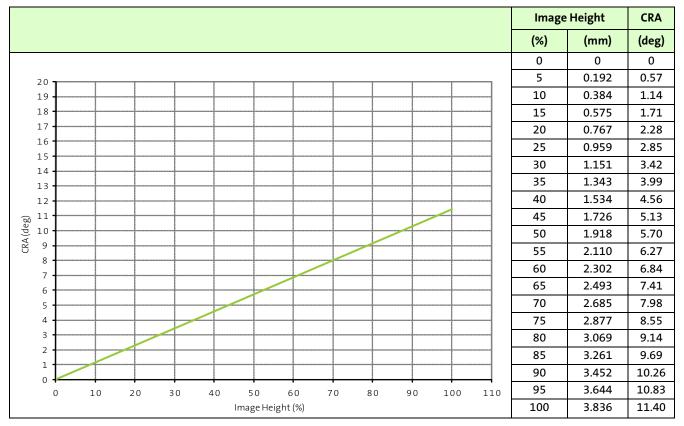

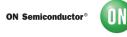

| Chief ray                      | angle                                                      | 0°, 11.4°, and 25°                                                                                                                                                                                                                      |  |

| Color filt                     | er array                                                   | RGB Bayer pattern                                                                                                                                                                                                                       |  |

| Shutter t                      | уре                                                        | Electronic rolling shutter (ERS) with global reset release (GRR)                                                                                                                                                                        |  |

| Input clo                      | ck frequency                                               | 2–64 MHz                                                                                                                                                                                                                                |  |

| Maxi-                          | Parallel                                                   | 96 Mp/s at 96 MHz PIXCLK                                                                                                                                                                                                                |  |

| mum<br>data<br>rate            | HiSPi (4-lane)                                             | 700 Mbps/lane                                                                                                                                                                                                                           |  |

|                                | 14M resolution<br>(4384H x 3288V)                          | Programmable up to 13.7 fps for HiSPi I/F, 6.3 fps for parallel I/F                                                                                                                                                                     |  |

| _                              | Preview VGA mode                                           | <ul><li> 30 fps with binning</li><li> 60 fps with skip2bin2</li></ul>                                                                                                                                                                   |  |

| Frame<br>rate                  | 1080p mode:                                                | <ul> <li>60 fps using HiSPi interface</li> <li>2304H x 1296V (1080p +20%EIS)</li> <li>30 fps using parallel interface</li> <li>2256H x 1268V (1080p +17%EIS)</li> </ul>                                                                 |  |

| ADC reso                       | lution                                                     | 12-bit, on-chip                                                                                                                                                                                                                         |  |

| Responsi                       | vity                                                       | 0.724 V/lux-sec (550nm)                                                                                                                                                                                                                 |  |

| Dynamic                        | range                                                      | 65.3 dB                                                                                                                                                                                                                                 |  |

| SNR <sub>MAX</sub>             | 0                                                          | 35.5 dB                                                                                                                                                                                                                                 |  |

|                                | I/O Digital                                                | 1.7–1.9 V (1.8 V nominal)<br>or 2.4–3.1 V (2.8 V nominal)                                                                                                                                                                               |  |

|                                | Digital                                                    | 1.7–1.9 V (1.8 V nominal)                                                                                                                                                                                                               |  |

| Supply                         | Analog                                                     | 2.7–3.1 V (2.8 V nominal)                                                                                                                                                                                                               |  |

| voltage                        | HISPI PHY<br>HISPI I/O (SLVS)<br>HISPI I/O (HIVCM)         | 1.7–1.9 V (1.8 V nominal)<br>0.3 - 0.9 V (0.4 or 0.8 V nominal)<br>1.7–1.9 V (1.8 V nominal)                                                                                                                                            |  |

| Power<br>Con-<br>sump-<br>tion | Full resolution 13.65<br>fps (HiSPi serial I/F,<br>12-bit) | 724 mW                                                                                                                                                                                                                                  |  |

|                                | 1080p60 (HiSPi serial<br>I/F, 10-bit)                      | XYbin2: 596 mW                                                                                                                                                                                                                          |  |

|                                | 1080p30 (HiSPi serial<br>I/F, 10-bit)                      | XYbin2: 443 mW                                                                                                                                                                                                                          |  |

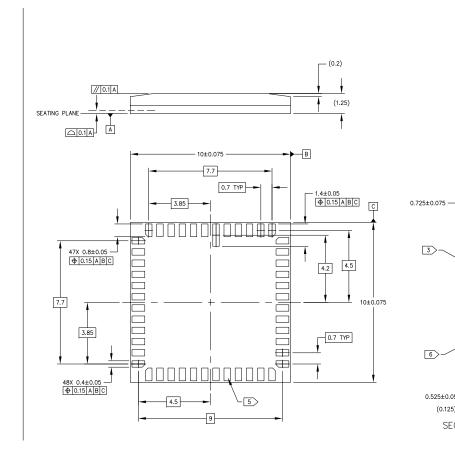

| Package                        |                                                            | 48-pin iLCC (10 mm x 10 mm) and bare die                                                                                                                                                                                                |  |

| Operating temperature          |                                                            | –30°C to +70°C (at junction)                                                                                                                                                                                                            |  |

# **Ordering Information**

## Table 2: Available Part Numbers

ON

| Part Number            | Product Description                 | Orderable Product Attribute Description |

|------------------------|-------------------------------------|-----------------------------------------|

| MT9F002I12STCV-DP      | RGB, 0deg CRA, HiSPi, iLCC Package  | Drypack, Protective Film                |

| MT9F002I12-N4000-DP    | RGB, 12deg CRA, HiSPi, iLCC Package | Drypack, Protective Film                |

| MT9F002I12STCVD3-GEVK  | 0deg CRA, HiSPi, Demo Kit           |                                         |

| MT9F002I12STCVH-GEVB   | Odeg CRA, HiSPi, Head Board         |                                         |

| MT9F002I12-N4000D-GEVK | 12deg CRA, HiSPi, Demo Kit          |                                         |

| MT9F002I12-N4000H-GEVB | 12deg CRA, HiSPi, Head Board        |                                         |

# **Table of Contents**

ON

| Features1                          |

|------------------------------------|

|                                    |

| Applications                       |

| General Description                |

| Ordering Information               |

| General Description                |

| Functional Overview                |

| Operating Modes                    |

| Signal Descriptions                |

| Output Data Format                 |

| HiSPi Physical Layer               |

| Comparison of SLVS and HiVCM17     |

| Two-Wire Serial Register Interface |

| Programming Restrictions           |

| Control of the Signal Interface    |

| Features                           |

| Sensor Readout Configuration       |

| Power Mode Contexts                |

| Sensor Core Digital Data Path      |

| Timing Specifications              |

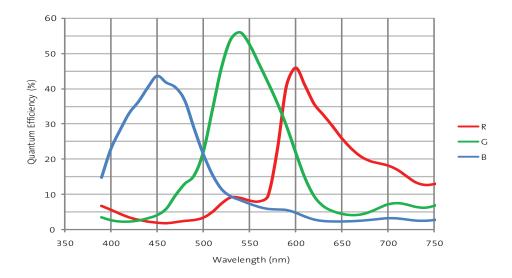

| Spectral Characteristics           |

| Electrical Characteristics         |

| Package Dimensions                 |

| Revision History                   |

# List of Figures

| Figure 1:  | Block Diagram                                                             |

|------------|---------------------------------------------------------------------------|

| Figure 2:  | Data Flow Diagram                                                         |

| Figure 3:  | Pixel Color Pattern Detail (Top Right Corner)                             |

| Figure 4:  | High-Resolution Still Image Capture + Full HD Video                       |

| Figure 5:  | Typical Configuration: Serial Four-Lane HiSPi Interface10                 |

| Figure 6:  | Typical Configuration: Parallel Pixel Data Interface                      |

| Figure 7:  | 48-Pin iLCC HiSPi Package Pinout Diagram14                                |

| Figure 8:  | Data Formats                                                              |

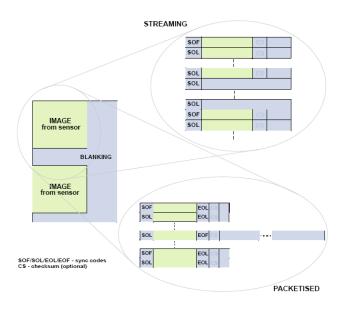

| Figure 9:  | Steaming vs. Packetized Transmission                                      |

| Figure 10: | HiSPi Transmitter and Receiver Interface Block Diagram17                  |

| Figure 11: | Timing Diagram                                                            |

| Figure 12: | Block Diagram of DLL Timing Adjustment                                    |

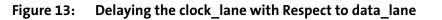

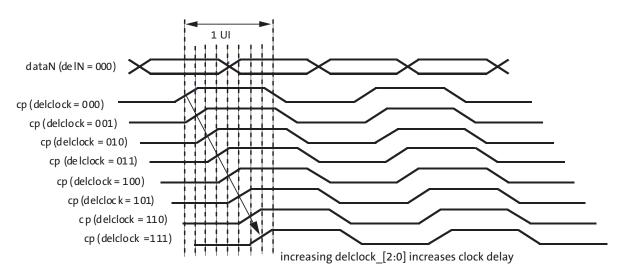

| Figure 13: | Delaying the clock_lane with Respect to data_lane                         |

| Figure 14: | Delaying data_lane with Respect to the clock_lane                         |

| Figure 15: | Spatial Illustration of Image Readout                                     |

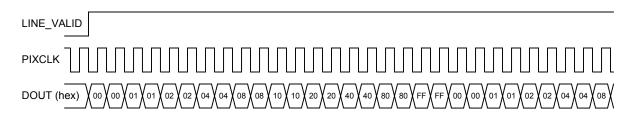

| Figure 16: | Pixel Data Timing Example                                                 |

| Figure 17: | Frame Timing and FV/LV Signals                                            |

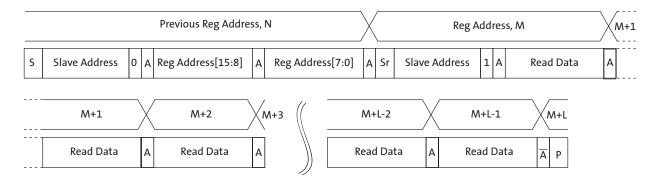

| Figure 18: | Single READ From Random Location                                          |

| Figure 19: | Single READ From Current Location                                         |

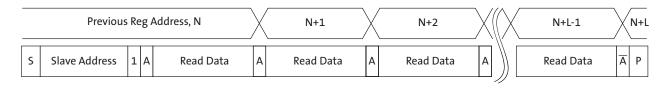

| Figure 20: | Sequential READ, Start From Random Location                               |

| Figure 21: | Sequential READ, Start From Current Location                              |

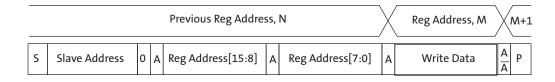

| Figure 22: | Single WRITE to Random Location                                           |

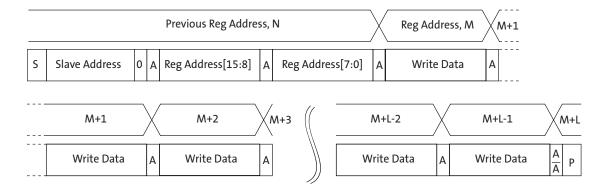

| Figure 23: | Sequential WRITE, Start at Random Location                                |

| Figure 24: | Effect of Limiter on the Data Path                                        |

| Figure 25: | Timing of Data Path                                                       |

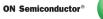

| Figure 26: | MT9F002 System States                                                     |

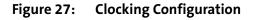

| Figure 27: | Clocking Configuration                                                    |

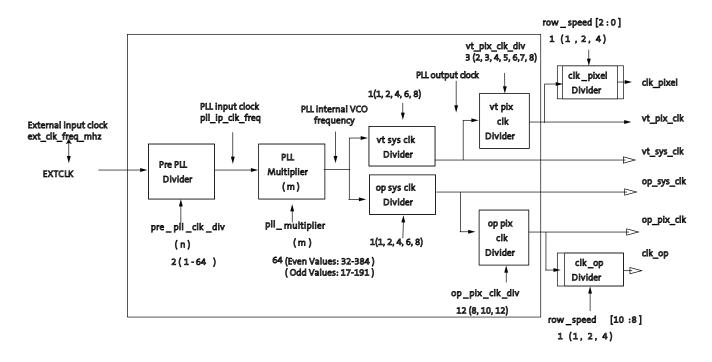

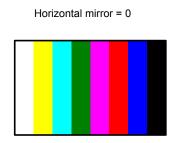

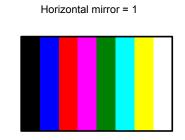

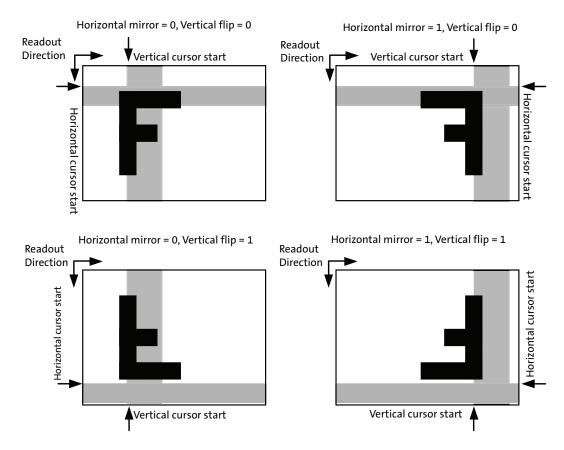

| Figure 28: | Effect of Horizontal Mirror on Readout Order                              |

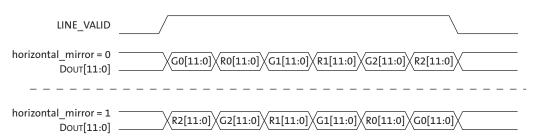

| Figure 29: | Effect of Vertical Flip on Readout Order43                                |

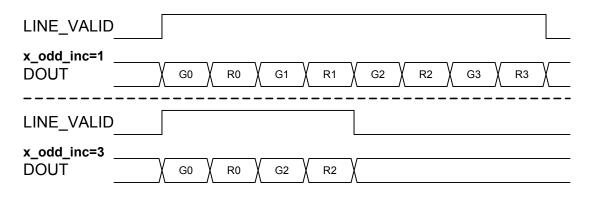

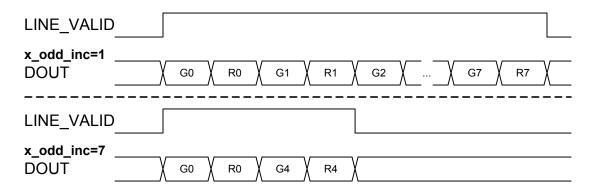

| Figure 30: | Effect of x odd inc=3 on readout sequence                                 |

| Figure 31: | Effect of x_odd_inc=7 on readout sequence                                 |

| Figure 32: | Pixel Readout (no subsampling)                                            |

| Figure 33: | Pixel Readout (x_odd_inc=3, y_odd_inc=1)                                  |

| Figure 34: | Pixel Readout (x_odd_inc=1, y_odd_inc=3)                                  |

| Figure 35: | Pixel Readout (x_odd_inc=3, y_odd_inc=3)                                  |

| Figure 36: | Pixel Readout (x_odd_inc=7, y_odd_inc=7)                                  |

| Figure 37: | Pixel Readout (x_odd_inc=7, y_odd_inc=15)                                 |

| Figure 38: | Pixel Readout (x_odd_inc=7, y_odd_inc=31)                                 |

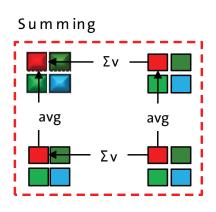

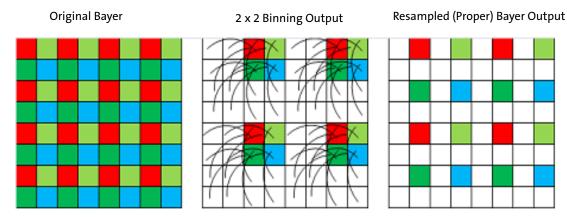

| Figure 39: | Pixel Binning and Summing                                                 |

| Figure 40: | Bayer Resampling                                                          |

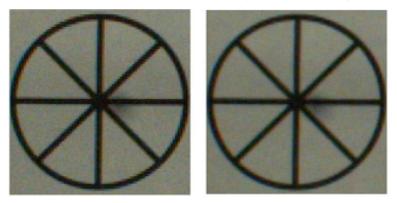

| Figure 41: | Results of Resampling                                                     |

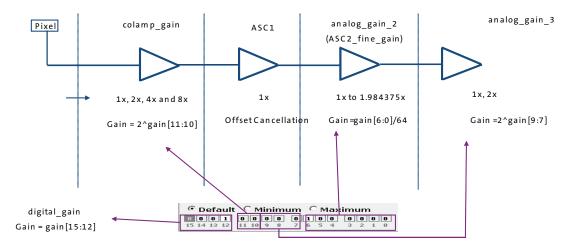

| Figure 42: | Analog Gain Stages                                                        |

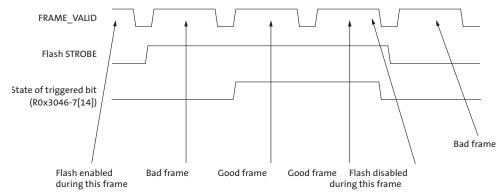

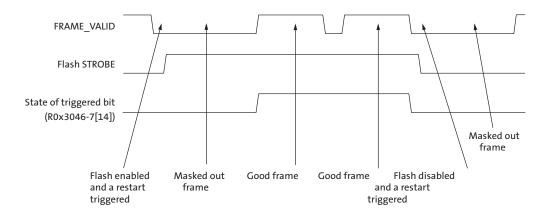

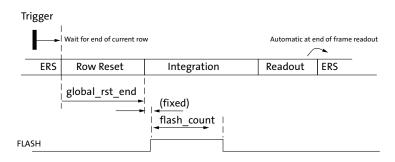

| Figure 43: | Xenon Flash Enabled                                                       |

| Figure 44: | LED Flash Enabled                                                         |

| Figure 45: | LED Flash Enabled Following Forced Restart                                |

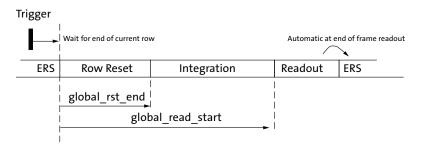

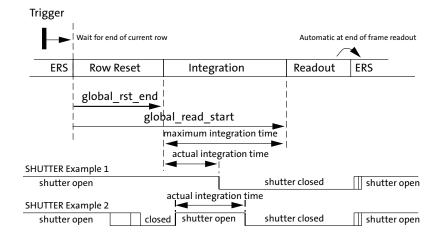

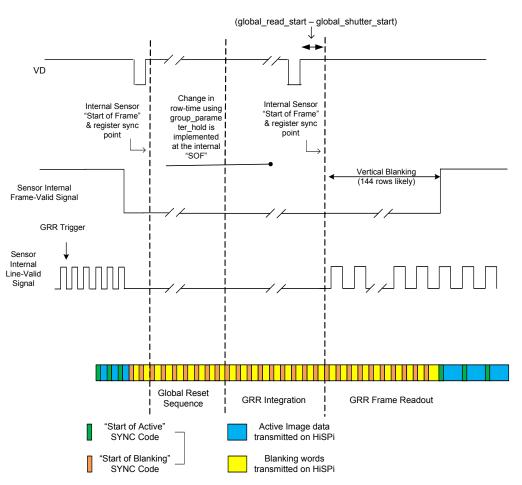

| Figure 46: | Overview of Global Reset Sequence                                         |

| Figure 47: | Entering and Leaving a Global Reset Sequence                              |

| Figure 48: | Controlling the Reset and Integration Phases of the Global Reset Sequence |

| Figure 49: | Control of the Electromechanical Shutter                                  |

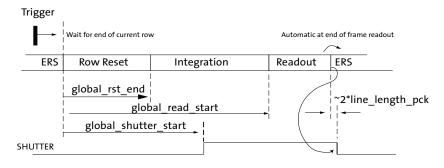

| Figure 50: | Controlling the SHUTTER Output                                            |

| Figure 51: | Using FLAŠH With Global Reset                                             |

| Figure 52: | Global Reset Bulb                                                         |

| Figure 53: | Entering Soft Standby During a Global Reset Sequence                      |

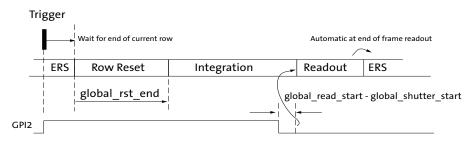

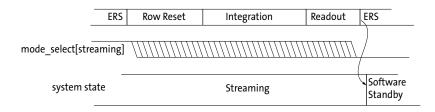

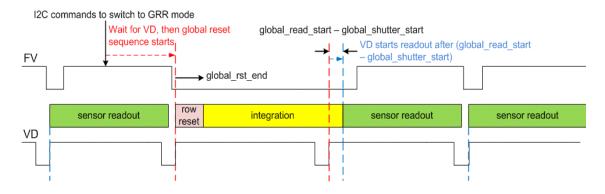

| Figure 54: | Slave Mode GRR Timing                                                     |

| Figure 55: | Slave Mode HiSPi Output (ERS to GRR Transition)                           |

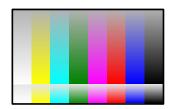

| Figure 56: | 100% Color Bars Test Pattern                                              |

| Figure 57: | Fade-to-Gray Color Bar Test Pattern         | 68 |

|------------|---------------------------------------------|----|

| Figure 58: | Walking 1s 12-Bit Pattern                   | 69 |

| Figure 59: | Walking 1s 10-Bit Pattern                   | 69 |

| Figure 60: | Walking 1s 8-Bit Pattern                    | 69 |

| Figure 61: | Test Cursor Behavior With Image Orientation | 70 |

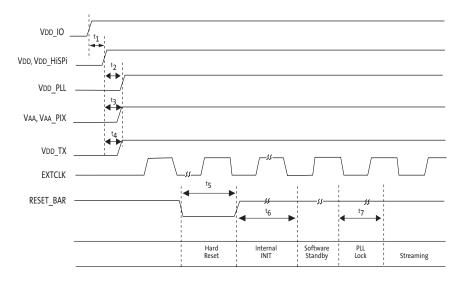

| Figure 62: | Power-Up Sequence                           | 71 |

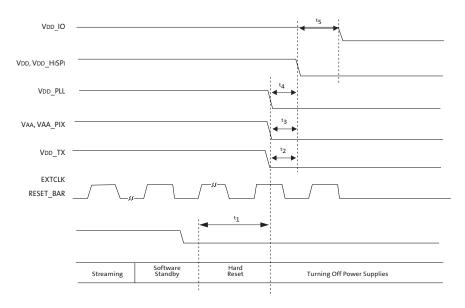

| Figure 63: | Power-Down Sequence                         | 72 |

| Figure 64: | Hard Standby and Hard Reset                 | 73 |

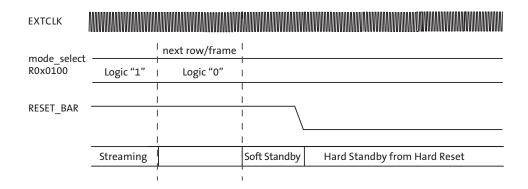

| Figure 65: | Soft Standby and Soft Reset                 | 74 |

| Figure 66: | Quantum Efficiency                          | 75 |

| Figure 67: | Two-Wire Serial Bus Timing Parameters       | 79 |

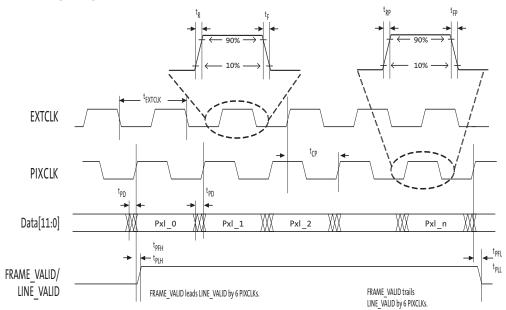

| Figure 68: | I/O Timing Diagram                          |    |

| Figure 69: | Single-Ended and Differential Signals       | 86 |

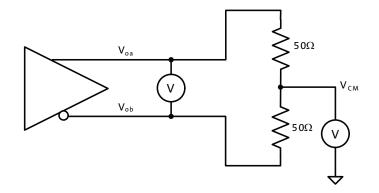

| Figure 70: | DC Test Circuit                             |    |

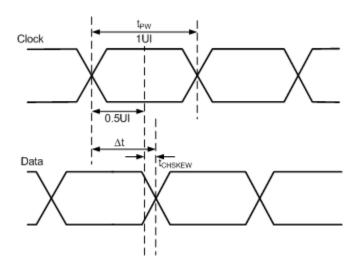

| Figure 71: | Clock-to-Data Skew Timing Diagram           | 87 |

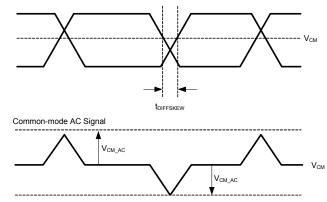

| Figure 72: | Differential Skew.                          | 88 |

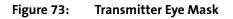

| Figure 73: | Transmitter Eye Mask                        | 88 |

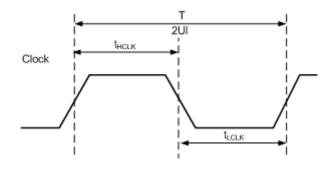

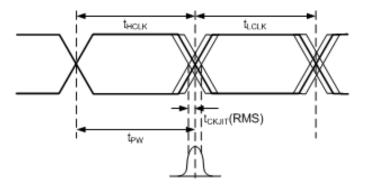

| Figure 74: | Clock Duty Cycle                            | 89 |

| Figure 75: | Clock Jitter                                | 89 |

| Figure 76: | 48-Pin iLCC Package Outline Drawing         | 91 |

|            |                                             |    |

# List of Tables

| Table 1:  | Key Performance Parameters                                    | 1 |

|-----------|---------------------------------------------------------------|---|

| Table 2:  | Available Part Numbers                                        |   |

| Table 3:  | Signal Descriptions                                           | 3 |

| Table 4:  | SLVS and HiVCM Comparison                                     | 7 |

| Table 5:  | Common Sensor Readout Modes                                   | 2 |

| Table 6:  | Definitions for Programming Rules                             | 8 |

| Table 7:  | Output Enable Control                                         |   |

| Table 8:  | Configuration of the Pixel Data Interface                     | 2 |

| Table 9:  | RESET_BAR and PLL in System States                            | 4 |

| Table 10: | Signal State During Reset                                     | 5 |

| Table 11: | Streaming/STANDBY                                             | 6 |

| Table 12: | Trigger Control                                               | 6 |

| Table 13: | PLL Parameter Range                                           |   |

| Table 14: | Minimum Row Time and Blanking Numbers                         |   |

| Table 15: | Minimum Frame Time and Blanking Numbers                       |   |

| Table 16: | Fine_Integration_Time Limits                                  |   |

| Table 17: | Fine_Correction Values                                        | 3 |

| Table 18: | Power Mode Contexts                                           |   |

| Table 19: | Recommended Register Settings                                 |   |

| Table 20: | Test Patterns                                                 |   |

| Table 21: | HiSPi Test Patterns                                           |   |

| Table 22: | Power-Up Sequence                                             | 1 |

| Table 23: | Power-Down Sequence                                           |   |

| Table 24: | 11.4° Chief Ray Angle                                         |   |

| Table 25: | 25° Chief Ray Angle                                           | 7 |

| Table 26: | CRA Value                                                     |   |

| Table 27: | DC Electrical Definitions and Characteristics                 |   |

| Table 28: | Absolute Maximum Ratings                                      |   |

| Table 29: | Two-Wire Serial Register Interface Electrical Characteristics |   |

| Table 30: | Two-Wire Serial Register Interface Timing Specification       |   |

| Table 31: | I/O Parameters                                                | 1 |

| Table 32: | I/O Timing                                                    |   |

| Table 33: | Power Supply and Operating Temperature                        |   |

| Table 34: | SLVS Electrical DC Specification                              |   |

| Table 35: | SLVS Electrical Timing Specification                          |   |

| Table 36: | HiVCM Power Supply and Operating Temperatures                 |   |

| Table 37: | HiVCM Electrical Voltage and Impedance Specification          |   |

| Table 38: | HiVCM Electrical AC Specification                             | 5 |

|           |                                                               |   |

# **General Description**

The MT9F002 digital image sensor features ON Semiconductor's breakthrough low-noise CMOS imaging technology that achieves near-CCD image quality (based on signal-to-noise ratio and low-light sensitivity) while maintaining the inherent size, cost, and integration advantages of CMOS.

When operated in its default 4:3 still-mode, the sensor generates a full resolution (4384x3288)image at 13 frames per second (fps) using the HiSPi serial interface. An on-chip analog-to-digital converter (ADC) generates a 12-bit value for each pixel.

# **Functional Overview**

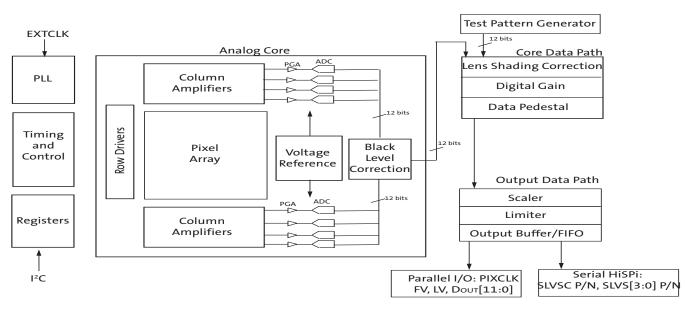

The MT9F002 is a progressive-scan sensor that generates a stream of pixel data at a constant frame rate. It uses an on-chip, phase-locked loop (PLL) to generate all internal clocks from a single master input clock running between 2 and 64 MHz. The maximum output pixel rate is 220 Mp/s for serial HiSPi I/F and 96 Mp/s for parallel I/F, corresponding to a pixel clock rate of 220 MHz and 96 MHz, respectively. A block diagram of the sensor is shown in Figure 1.

# Figure 1: Block Diagram

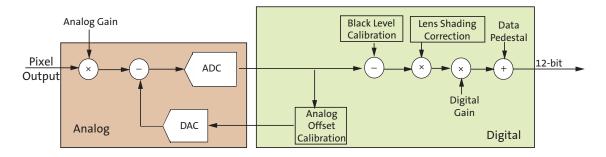

The core of the sensor is a 14Mp active-pixel array. The timing and control circuitry sequences through the rows of the array, resetting and then reading each row in turn. In the time interval between resetting a row and reading that row, the pixels in the row integrate incident light. The exposure is controlled by varying the time interval between reset and readout. Once a row has been read, the data from the columns is sequenced through an analog signal chain (providing offset correction and gain), and then through an ADC. The output from the ADC is a 12-bit value for each pixel in the array. The ADC output passes through a digital processing signal chain (which provides further data path corrections and applies digital gain).

The pixel array contains optically active and light-shielded ("dark") pixels. The dark pixels are used to provide data for on-chip offset-correction algorithms ("black level" control).

The image black level is calibrated to compensate for analog offset and ensure that the ADC range is utilized well. It also reduces row noise in the image. The black level in the output image involves Fine Digital Correction and addition of Data Pedestal (42 LSB for 10-bit ADC, 168 LSB for 12-bit ADC)

#### Figure 2: Data Flow Diagram

The sensor contains a set of control and status registers that can be used to control many aspects of the sensor behavior including the frame size, exposure, and gain setting. These registers can be accessed through a two-wire serial interface.

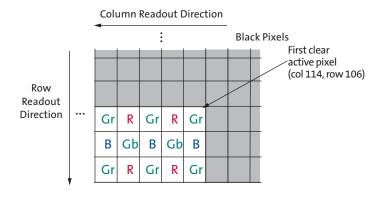

The output from the sensor is a Bayer pattern; alternate rows are a sequence of either green and red pixels or blue and green pixels. The offset and gain stages of the analog signal chain provide per-color control of the pixel data.

The control registers, timing and control, and digital processing functions shown in Figure 1 on page 7 are partitioned into three logical parts:

- A sensor core that provides array control and data path corrections. The output of the sensor core is a 12-bit parallel pixel data stream qualified by an output data clock (PIXCLK), together with LINE\_VALID (LV) and FRAME\_VALID (FV) signals or a 4-lane serial high-speed pixel interface (HiSPi).

- A digital shading correction block to compensate for color/brightness shading introduced by the lens or chief ray angle (CRA) curve mismatch.

- Additional functionality is provided. This includes a horizontal and vertical image scaler, a limiter, an output FIFO, and a serializer.

The output FIFO is present to prevent data bursts by keeping the data rate continuous. Programmable slew rates are also available to reduce the effect of electromagnetic interference from the output interface.

A flash output signal is provided to allow an external xenon or LED light source to synchronize with the sensor exposure time. Additional I/O signals support the provision of an external mechanical shutter.

## **Pixel Array**

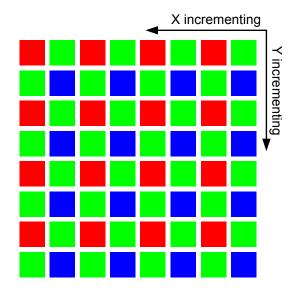

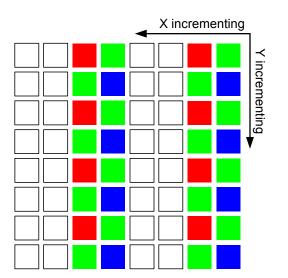

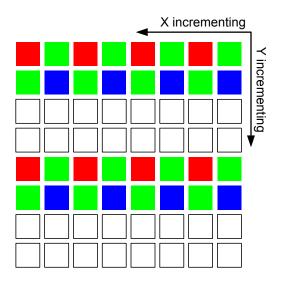

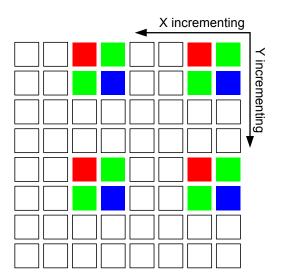

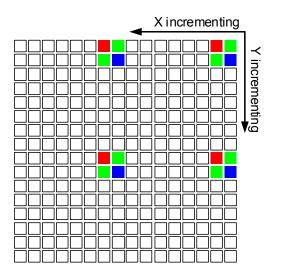

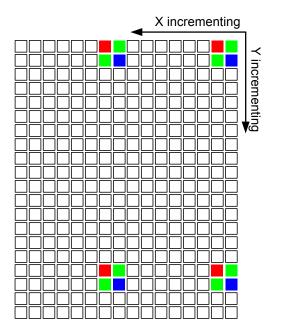

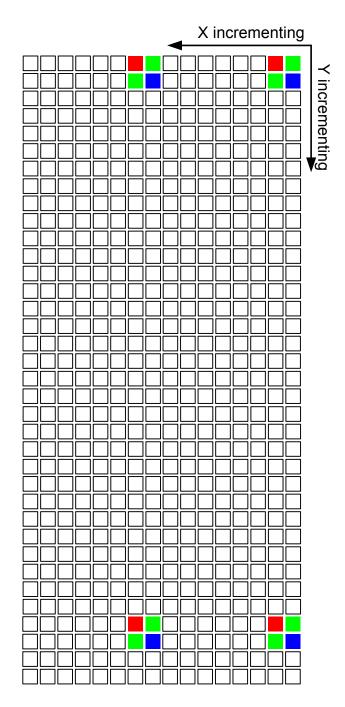

The sensor core uses a Bayer color pattern, as shown in Figure 3. The even-numbered rows contain green and red pixels; odd-numbered rows contain blue and green pixels. Even-numbered columns contain green and blue pixels; odd-numbered columns contain red and green pixels.

# Figure 3: Pixel Color Pattern Detail (Top Right Corner)

## Figure 4: High-Resolution Still Image Capture + Full HD Video

# **Operating Modes**

By default, the MT9F002 powers up with the serial pixel data interface enabled. The sensor can operate in serial HiSPi or parallel mode.

For low-noise operation, the MT9F002 requires separate power supplies for analog and digital power. Incoming digital and analog ground conductors should be placed in such a way that coupling between the two are minimized. Both power supply rails should also be routed in such a way that noise coupling between the two supplies and ground is minimized.

# Caution ON Semiconductor does not recommend the use of inductance filters on the power supplies or output signals.

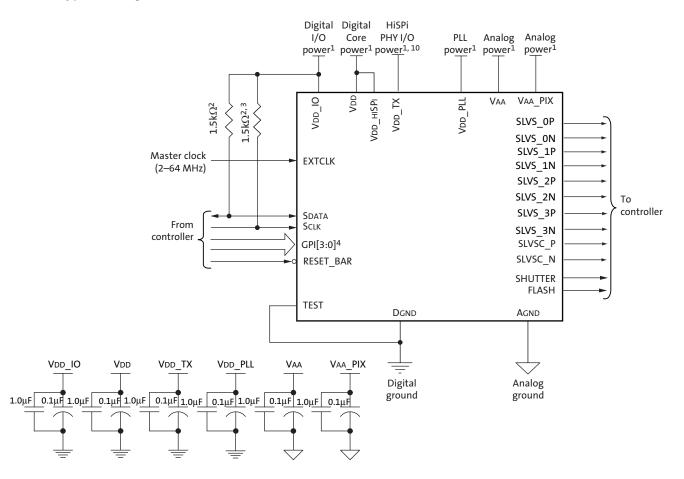

#### Figure 5: Typical Configuration: Serial Four-Lane HiSPi Interface

Notes: 1. All power supplies should be adequately decoupled. ON Semiconductor recommends having 1.0µF and 0.1µF decoupling capacitors for every power supply.

- 2. ON Semiconductor recommends a resistor value of  $1.5 k\Omega$ , but a greater value may be used for slower two-wire speed.

- 3. This pull-up resistor is not required if the controller drives a valid logic level on SCLK at all times.

- 4. The GPI pins can be statically pulled HIGH or LOW and can be programmed to perform special functions (TRIGGER/VD, OE\_BAR, SADDR, STANDBY) to be dynamically controlled. GPI pads can be left floating, when not used.

- 5. VPP, which is not shown in Figure 5, is left unconnected during normal operation.

- 6. The parallel interface output pads can be left unconnected when the serial output interface is used.

- ON Semiconductor recommends that 0.1μF and 10μF decoupling capacitors for each power supply are mounted as close as possible to the pad. Actual values and results may vary depending on layout and design considerations. Check the MT9F002 demo headboard schematics for circuit recommendations.

- 8. TEST signals must be tied to DGND for normal sensor operation.

- 9. ON Semiconductor recommends that analog power planes are placed in a manner such that coupling with the digital power planes is minimized.

- 10. For serial HiSPi HiVCM mode, set register bit R0x306E[9] = 1 and VDD\_TX = VDD\_IO = 1.8V.

#### Figure 6: Typical Configuration: Parallel Pixel Data Interface

- Notes: 1. All power supplies should be adequately decoupled. ON Semiconductor recommends having 1.0μF and 0.1μF decoupling capacitors for every power supply.

- 2. ON Semiconductor recommends a resistor value of  $1.5k\Omega$ , but a greater value may be used for slower two-wire speed.

- 3. This pull-up resistor is not required if the controller drives a valid logic level on SCLK at all times.

- 4. The GPI pins can be statically pulled HIGH or LOW and can be programmed to perform special functions (TRIGGER/VD, OE\_BAR, SADDR, STANDBY) to be dynamically controlled. GPI pads can be left floating, when not used.

- 5. VPP, which is not shown in Figure 6, is left unconnected during normal operation.

- The serial interface output pads can be left unconnected when the parallel output interface is used.

ON Semiconductor recommends that 0.1μF and 10μF decoupling capacitors for each power supply are mounted as close as possible to the pad. Actual values and results may vary depending on layout and design considerations. Check the MT9F002 demo headboard schematics for circuit recommendations.

- 8. TEST signals must be tied to DGND for normal sensor operation.

9. ON Semiconductor recommends that analog power planes are placed in a manner such that coupling with the digital power planes is minimized.

# **Signal Descriptions**

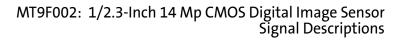

Table 3 provides signal descriptions for MT9F002 die. For pad location and aperture information, refer to the MT9F002 die data sheet.

## Table 3:Signal Descriptions

ON

| Signal    | Туре   | Description                                                                                                                                                                                                                                                                                                                                                                        |  |

|-----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| EXTCLK    | Input  | Master clock input, 2-64 MHz.                                                                                                                                                                                                                                                                                                                                                      |  |

| RESET_BAR | Input  | Asynchronous active LOW reset. When asserted, data output stops and all internal registers are restored to their factory default settings.                                                                                                                                                                                                                                         |  |

| Sclk      | Input  | Serial clock for access to control and status registers.                                                                                                                                                                                                                                                                                                                           |  |

| GPI[3:0]  | Input  | General purpose inputs. After reset, these pads are powered-down by default;<br>this means that it is not necessary to bond to these pads. Any of these pads<br>can be programmed (through register R0x3026) to provide hardware control<br>of the standby, output enable, SADDR select, shutter trigger or slave mode<br>trigger (VD) function. Can be left floating if not used. |  |

| TEST      | Input  | Enable manufacturing test modes. Tie to DGND for normal sensor operation.                                                                                                                                                                                                                                                                                                          |  |

| Sdata     | I/O    | Serial data from READs and WRITEs to control and status registers.                                                                                                                                                                                                                                                                                                                 |  |

| Vpp       | Supply | Disconnect pad for normal operation.<br>Power supply used to program one-time programmable (OTP) memory.<br>Manufacturing use only.                                                                                                                                                                                                                                                |  |

| Vdd_HiSPi | Supply | HiSPi PHY power supply. Digital power supply for the HiSPi serial data interface. This should be tied to VDD.                                                                                                                                                                                                                                                                      |  |

| VDD_TX    | Supply | Digital power supply for the HiSPi I/O.<br>For HiSPi SLVS mode, set register bit R0x306E[9] = 0 (default), and<br>VDD_TX to 0.4V.<br>For HiSPi HiVCM mode, set register bit R0x306E[9] = 1, and VDD_TX =<br>VDD_IO.                                                                                                                                                                |  |

| VAA       | Supply | Analog power supply.                                                                                                                                                                                                                                                                                                                                                               |  |

| VAA_PIX   | Supply | Analog power supply for the pixel array.                                                                                                                                                                                                                                                                                                                                           |  |

| Agnd      | Supply | Analog ground.                                                                                                                                                                                                                                                                                                                                                                     |  |

| Vdd       | Supply | Digital power supply.                                                                                                                                                                                                                                                                                                                                                              |  |

| VDD_IO    | Supply | I/O power supply.                                                                                                                                                                                                                                                                                                                                                                  |  |

| Dgnd      | Supply | Common ground for digital and I/O.                                                                                                                                                                                                                                                                                                                                                 |  |

| VDD_PLL   | Supply | PLL power supply.                                                                                                                                                                                                                                                                                                                                                                  |  |

| SLVS_OP   | Output | Lane 1 differential HiSPi (SLVS) serial data (positive). Qualified by the SLVS serial clock.                                                                                                                                                                                                                                                                                       |  |

| SLVS_0N   | Output | Lane 1 differential HiSPi (SLVS) serial data (negative). Qualified by the SLVS serial clock.                                                                                                                                                                                                                                                                                       |  |

| SLVS_1P   | Output | Lane 2 differential HiSPi (SLVS) serial data (positive). Qualified by the SLVS serial clock.                                                                                                                                                                                                                                                                                       |  |

| SLVS_1N   | Output | Lane 2 differential HiSPi (SLVS) serial data (negative). Qualified by the SLVS serial clock.                                                                                                                                                                                                                                                                                       |  |

| SLVS_2P   | Output | Lane 3 differential HiSPi (SLVS) serial data (positive). Qualified by the SLVS serial clock.                                                                                                                                                                                                                                                                                       |  |

| SLVS_2N   | Output | Lane 3 differential HiSPi (SLVS) serial data (negative). Qualified by the SLVS serial clock.                                                                                                                                                                                                                                                                                       |  |

| SLVS_3P   | Output | Lane 4 differential HiSPi (SLVS) serial data (positive). Qualified by the SLVS serial clock.                                                                                                                                                                                                                                                                                       |  |

| Table 3: | Signal Descriptions | (continued) |

|----------|---------------------|-------------|

|----------|---------------------|-------------|

| Signal      | Туре   | Description                                                                                      |

|-------------|--------|--------------------------------------------------------------------------------------------------|

| SLVS_3N     | Output | Lane 4 differential HiSPi (SLVS) serial data (negative). Qualified by the SLVS serial clock.     |

| SLVS_CP     | Output | Differential HiSPi (SLVS) serial clock (positive). Qualified by the SLVS serial clock.           |

| SLVS_CN     | Output | Differential HiSPi (SLVS) serial clock (negative). Qualified by the SLVS serial clock.           |

| LINE_VALID  | Output | LINE_VALID (LV) output. Qualified by PIXCLK.                                                     |

| FRAME_VALID | Output | FRAME_VALID (FV) output. Qualified by PIXCLK.                                                    |

| Dout[11:0]  | Output | Parallel pixel data output. Qualified by PIXCLK.                                                 |

| PIXCLK      | Output | Pixel clock. Used to qualify the LV, FV, and DOUT[11:0] outputs.                                 |

| FLASH       | Output | Flash output. Synchronization pulse for external light source. Can be left floating if not used. |

| SHUTTER     | Output | Control for external mechanical shutter. Can be left floating if not used.                       |

# Figure 7: 48-Pin iLCC HiSPi Package Pinout Diagram

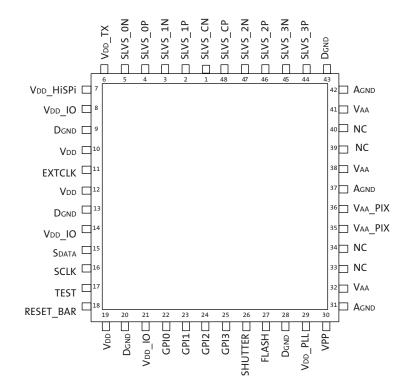

# **Output Data Format**

# **Pixel Data Interface**

The MT9F002 reads data out of the pixel array in a progressive scan over a High Speed serial data interface, or parallel data interface. RAW8, RAW10, and RAW12 image data formats are supported.

#### Figure 8: Data Formats

## **High Speed Serial Pixel Data Interface**

The High Speed Serial Pixel (HiSPi)<sup>TM</sup> interface uses four data and one clock low voltage differential signaling (SLVS) outputs.

- SLVS\_CP

- SLVS\_CN

- SLVS\_0P

- SLVS\_0N

- SLVS\_1P

- SLVS 1N

- SLVS\_2P

- SLVS\_2N

- SLVS\_3P

- SLVS\_3N

The HiSPi interface supports the following protocols: Streaming-S and Packetized-SP. The streaming protocol conforms to a standard video application where each line of active or intra-frame blanking provided by the sensor is transmitted at the same length. The packetized protocol will transmit only the active data ignoring line-to-line and frame-to-frame blanking data.

#### **HiSPi Streaming Mode Protocol Layer**

The protocol layer is positioned between the output data path of the sensor and the physical layer. The main functions of the protocol layer are generating sync codes, formatting pixel data, inserting horizontal/vertical blanking codes, and distributing pixel data over defined data lanes.

The HiSPi interface can only be configured when the sensor is in standby. This includes configuring the interface to transmit across 1, 2, or all 4 data lanes.

## **Protocol Fundamentals**

Referring to Figure 9, it can be seen that a SYNC code is inserted in the serial data stream prior to each line of image data. The streaming protocol will insert a SYNC code to transmit each active data line and vertical blanking lines.

The packetized protocol will transmit a SYNC code to note the start and end of each row. The packetized protocol uses sync a "Start of Frame" (SOF) sync code at the start of a frame and a "Start of Line" (SOL) sync code at the start of a line within the frame. The protocol will also transmit an "End of Frame" (EOF) at the end of a frame and an "End of Line" (EOL) sync code at the end of a row within the frame

#### Figure 9: Steaming vs. Packetized Transmission

See the High-Speed Serial Pixel (HiSPi)™ Protocol Specification V1.00.00 for HiSPi details.

# **HiSPi Physical Layer**

The HiSPi physical layer is partitioned into blocks of four data lanes and an associated clock lane. Any reference to the PHY in the remainder of this document is referring to this minimum building block.

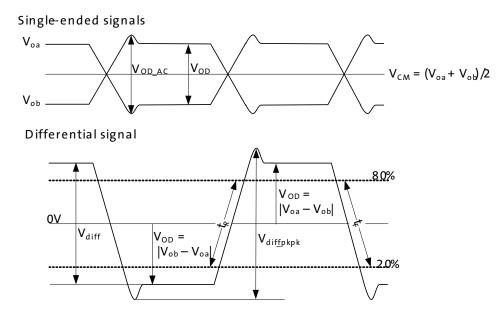

The HiSPi PHY uses a low voltage serial differential output. The HiSPi PHY drivers use a simple current steering driver scheme with two outputs that are complementary to each other (VOA and VOB). It is intended that these drivers be attached to short-length  $100\Omega$  differential interconnect to a receiver with a  $100\Omega$  termination. CL represents the total parasitic excess capacitance loading of the receiver and the interconnect.

There are two standards:

• Scalable Low Voltage Serial (SLVS) which has low amplitude and common-mode voltage (VCM) but scalable using an external supply.

• High VCM scalable serial interface (HiVCM), which has larger scalable amplitude and a high common-mode voltage.

**ON Semiconductor®**

Here is a comparison of the differences between SLVS and HiVCM.

| Parameter                                   | HiVCM           | SLVS           |

|---------------------------------------------|-----------------|----------------|

| Typical Differential Amplitude <sup>1</sup> | 280mV           | 200mV          |

| Typical Common Mode <sup>1</sup>            | 0.9V            | 200mV          |

| Typical Power Consumption <sup>2</sup>      | 45mW            | 4mW            |

| Transmission Distance                       | Longer distance | Short distance |

| LVDS FPGA Receiver<br>Compatible            | Yes             | No             |

#### Table 4: SLVS and HiVCM Comparison

#### Notes: 1. These are nominal values

2. Power from load driving stage, digital/serializer logic (VDD\_HiSPi) not included.

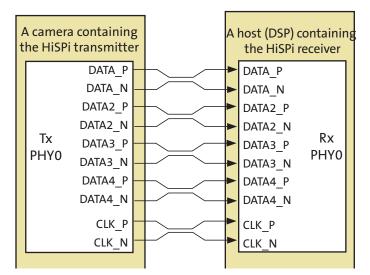

The HiSPi interface building block is a unidirectional differential serial interface with four data and one double data rate (DDR) clock lanes. The four Data lanes are 90 degrees out of phase with the Clock lanes. One clock for every four serial data lanes is provided for phase alignment across multiple lanes. Figure 10 shows the configuration between the HiSPi transmitter and the receiver.

## Figure 10: HiSPi Transmitter and Receiver Interface Block Diagram

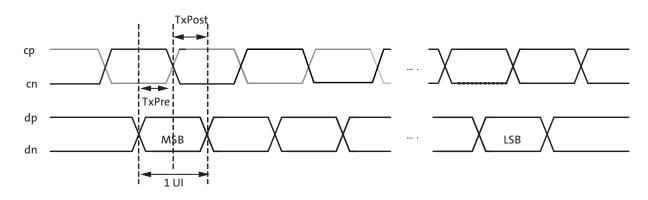

The PHY will serialize a 10-, 12-, 14- or 16-bit data word and transmit each bit of data centered on a rising edge of the clock, the second on the falling edge of clock. Figure 11 shows bit transmission. In this example, the word is transmitted in order of MSB to LSB. The receiver latches data at the rising and falling edge of the clock.

# Figure 11: Timing Diagram

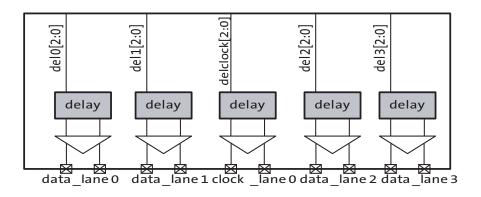

#### **DLL Timing Adjustment**

The specification includes a DLL to compensate for differences in group delay for each data lane. The DLL is connected to the clock lane and each data lane, which acts as a control master for the output delay buffers. Once the DLL has gained phase lock, each lane can be delayed in 1/8 unit interval (UI) steps. This additional delay allows the user to increase the setup or hold time at the receiver circuits and can be used to compensate for skew introduced in PCB design.

If the DLL timing adjustment is not required, the data and clock lane delay settings should be set to a default code of 0x000 to reduce jitter, skew, and power dissipation.

#### Figure 12: Block Diagram of DLL Timing Adjustment

## Figure 14: Delaying data\_lane with Respect to the clock\_lane

## **Parallel Pixel Data Interface**

MT9F002 image data is read out in a progressive scan. Valid image data is surrounded by horizontal blanking and vertical blanking, as shown in Figure 15. The amount of horizontal blanking and vertical blanking is programmable; LV is HIGH during the shaded region of the figure. FV timing is described in the "Output Data Timing (Parallel Pixel Data Interface)".

# Figure 15: Spatial Illustration of Image Readout

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                              | 00 00 00 00 00 00<br>00 00 00 00 00 00       |

|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------|

| VALID IMAGE                                                                                                         | HORIZONTAL<br>BLANKING                       |

| $\begin{array}{c} P_{m-1,0} \ P_{m-1,1}P_{m-1,n-1} \ P_{m-1,n} \\ P_{m,0} \ P_{m,1}P_{m,n-1} \ P_{m,n} \end{array}$ | 00 00 00 00 00 00<br>00 00 00 00 00 00       |

| 00 00 00 00 00 00 00 00 00 00 00 0                                                                                  | 00 00 00 00 00 00 00<br>00 00 00 00 00 00 00 |

| VERTICAL BLANKING                                                                                                   | VERTICAL/HORIZONTAL<br>BLANKING              |

| 00 00 00 00 00 00<br>00 00 00                                                                                       | 00 00 00                                     |

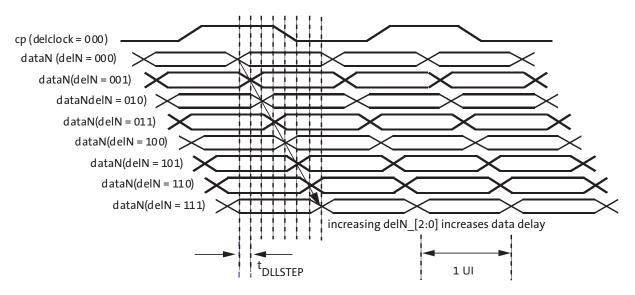

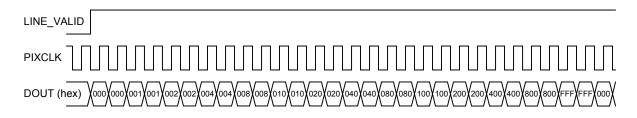

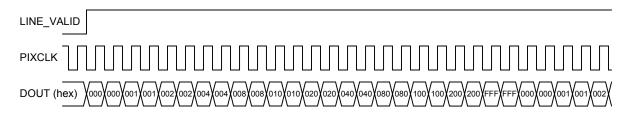

# **Output Data Timing (Parallel Pixel Data Interface)**

MT9F002 output data is synchronized with the PIXCLK output. When LV is HIGH, one pixel value is output on the 12-bit DOUT output every PIXCLK period. The pixel clock frequency can be determined based on the sensor's master input clock and internal PLL configuration. The rising edges on the PIXCLK signal occurs one-half of a pixel clock period after transitions on LV, FV, and DOUT (see Figure 16). This allows PIXCLK to be used as a clock to sample the data. PIXCLK is continuously enabled, even during the blanking period. The MT9F002 can be programmed to delay the PIXCLK edge relative to the DOUT transitions. This can be achieved by programming the corresponding bits in the row\_speed register.

#### Figure 16: Pixel Data Timing Example

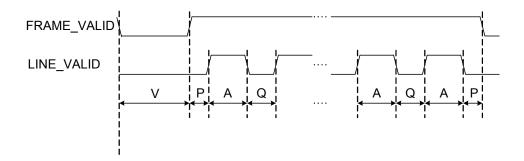

## Figure 17: Frame Timing and FV/LV Signals

The sensor timing is shown in terms of pixel clock cycles (see Figure 16 on page 21). The default settings for the on-chip PLL generate a pixel array clock (vt\_pix\_clk) of 110 MHz and an output clock (op\_pix\_clk) of 55 MHz given a 24 MHz input clock to the MT9F002. Equations for calculating the frame rate are given in "Frame Rate Control" on page 51.

| Table 5: Common Sensor Readout Mo | des |

|-----------------------------------|-----|

|-----------------------------------|-----|

| Key Readout<br>Modes          | Output Resolution | Aspect<br>Ratio | DFOV: 7.67<br>mm (%) | Subsampling<br>Mode     | Frame<br>Rate | ADC Effective<br>Bit-Depth | Data Rate<br>(Mbps/Lane) |

|-------------------------------|-------------------|-----------------|----------------------|-------------------------|---------------|----------------------------|--------------------------|

| 14M Capture                   | 4384H x 3288V     | (4:3)           | 100                  | n/a                     | 13.7          | 12                         | 660                      |

| 1080p<br>+20% EIS (3Mp)       | 2304H x 1296V     | (16:9)          | 96                   | x: Bin2<br>y: Bin2      | 60            | 10                         | 550                      |

| Video                         | 2304H x 1296V     | (16:9)          | 96                   | x: Bin2<br>y: Bin2      | 30            | 10                         | 275                      |

| 720p<br>+20%EIS (1.3Mp)       | 1536H x 864V      | (16:9)          | 64                   | x: Bin2<br>y: Bin2      | 60            | 10                         | 550                      |

| Video                         | 1536H x 864V      | (16:9)          | 64                   | x: Bin2<br>y: Bin2      | 30            | 10                         | 275                      |

| VGA Video (High<br>Quality)   | 1096H x 822V      | (4:3)           | 100                  | x: Skip2Bin2<br>y: Bin4 | 60            | 10                         | 550                      |

| EVF1 - Preview<br>(Low Power) | 1096H x 822V      | (4:3)           | 100                  | x: Skip2Bin2<br>y: Bin4 | 30            | 10                         | 275                      |

| EVF2 - Preview<br>(Low Power) | 1152H x 648V      | (16:9)          | 96                   | x: Skip2Bin2<br>y: Bin4 | 30            | 10                         | 275                      |

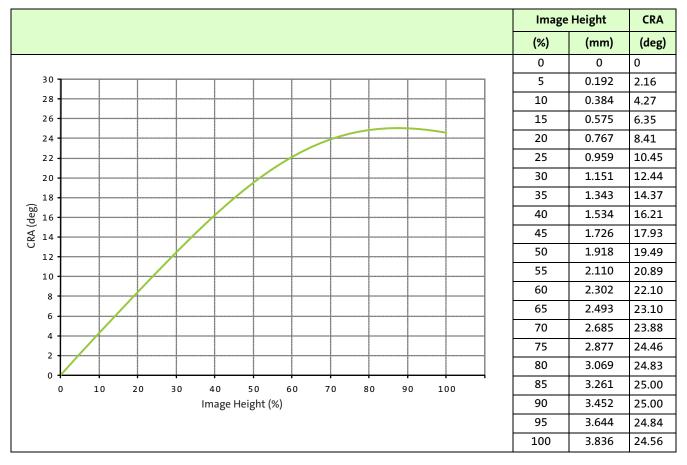

# **Two-Wire Serial Register Interface**

ON

|                         | -8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | The two-wire serial interface bus enables read/write access to control and status regis-<br>ters within the MT9F002. The interface protocol uses a master/slave model in which a<br>master controls one or more slave devices. The sensor acts as a slave device. The master<br>generates a clock (SCLK) that is an input to the sensor and is used to synchronize trans-<br>fers. Data is transferred between the master and the slave on a bidirectional signal<br>(SDATA). SDATA is pulled up to VDD_IO off-chip by a $1.5k\Omega$ resistor. Either the slave or<br>master device can drive SDATA LOW—the interface protocol determines which device is<br>allowed to drive SDATA at any given time. |

|                         | The protocols described in the two-wire serial interface specification allow the slave device to drive SCLK LOW; the MT9F002 uses SCLK as an input only and therefore never drives it LOW.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Protocol                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                         | Data transfers on the two-wire serial interface bus are performed by a sequence of low-<br>level protocol elements:<br>1. a (repeated) start condition<br>2. a slave address/data direction byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                         | 3. an (a no-) acknowledge bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                         | <ol> <li>a message byte</li> <li>a stop condition</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                         | The bus is idle when both SCLK and SDATA are HIGH. Control of the bus is initiated with a start condition, and the bus is released with a stop condition. Only the master can generate the start and stop conditions.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Start Condition         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                         | A start condition is defined as a HIGH-to-LOW transition on SDATA while SCLK is HIGH.<br>At the end of a transfer, the master can generate a start condition without previously<br>generating a stop condition; this is known as a "repeated start" or "restart" condition.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Stop Condition          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                         | A stop condition is defined as a LOW-to-HIGH transition on SDATA while SCLK is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Data Transfer           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                         | Data is transferred serially, 8 bits at a time, with the MSB transmitted first. Each byte of data is followed by an acknowledge bit or a no-acknowledge bit. This data transfer mechanism is used for both the slave address/data direction byte and for message bytes.                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                         | One data bit is transferred during each SCLK clock period. SDATA can change when SCLK is LOW and must be stable while SCLK is HIGH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Slave Address/Data Dire | ction Byte                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                         | Bits [7:1] of this byte represent the device slave address and bit [0] indicates the data transfer direction. A "0" in bit [0] indicates a WRITE, and a "1" indicates a READ. The default slave addresses used by the MT9F002 sensor are 0x20 (write address) and 0x21 (read address). Alternative slave addresses of 0x30 (write address) and 0x31 (read address) can be selected by enabling and asserting the SADDR signal through the GPI nin                                                                                                                                                                                                                                                       |

pin.

|                    | Alternate slave addresses can also be programmed through the i2c_ids register (R0x31FC-31FD). Note that this register needs to be unlocked through reset_register_lock_reg (R0x301A[3]) before is can be written to                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Message Byte       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    | Message bytes are used for sending register addresses and register write data to the slave device and for retrieving register read data.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Acknowledge Bit    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    | Each 8-bit data transfer is followed by an acknowledge bit or a no-acknowledge bit in the SCLK clock period following the data transfer. The transmitter (which is the master when writing, or the slave when reading) releases SDATA. The receiver indicates an acknowledge bit by driving SDATA LOW. As for data transfers, SDATA can change when SCLK is LOW and must be stable while SCLK is HIGH.                                                                                                                                                                                                |

| No-Acknowledge Bit |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    | The no-acknowledge bit is generated when the receiver does not drive SDATA LOW during the SCLK clock period following a data transfer. A no-acknowledge bit is used to terminate a read sequence.                                                                                                                                                                                                                                                                                                                                                                                                     |

| Typical Sequence   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                    | A typical READ or WRITE sequence begins by the master generating a start condition on<br>the bus. After the start condition, the master sends the 8-bit slave address/data direction<br>byte. The last bit indicates whether the request is for a read or a write, where a "0" indi-<br>cates a write and a "1" indicates a read. If the address matches the address of the slave<br>device, the slave device acknowledges receipt of the address by generating an acknowl-<br>edge bit on the bus.                                                                                                   |

|                    | If the request was a WRITE, the master then transfers the 16-bit register address to which<br>the WRITE should take place. This transfer takes place as two 8-bit sequences and the<br>slave sends an acknowledge bit after each sequence to indicate that the byte has been<br>received. The master then transfers the data as an 8-bit sequence; the slave sends an<br>acknowledge bit at the end of the sequence. The master stops writing by generating a<br>(re)start or stop condition.                                                                                                         |

|                    | If the request was a READ, the master sends the 8-bit write slave address/data direction<br>byte and 16-bit register address, the same way as with a WRITE request. The master then<br>generates a (re)start condition and the 8-bit read slave address/data direction byte, and<br>clocks out the register data, eight bits at a time. The master generates an acknowledge<br>bit after each 8-bit transfer. The slave's internal register address is automatically incre-<br>mented after every 8 bits are transferred. The data transfer is stopped when the master<br>sends a no-acknowledge bit. |

# Single READ From Random Location

This sequence (Figure 18) starts with a dummy WRITE to the 16-bit address that is to be used for the READ. The master terminates the WRITE by generating a restart condition. The master then sends the 8-bit read slave address/data direction byte and clocks out one byte of register data. The master terminates the READ by generating a no-acknowl-edge bit followed by a stop condition. Figure 18 shows how the internal register address maintained by the MT9F002 is loaded and incremented as the sequence proceeds.

#### Figure 18: Single READ From Random Location

# Single READ From Current Location

This sequence (Figure 19) performs a read using the current value of the MT9F002 internal register address. The master terminates the READ by generating a no-acknowledge bit followed by a stop condition. The figure shows two independent READ sequences.

#### Figure 19: Single READ From Current Location

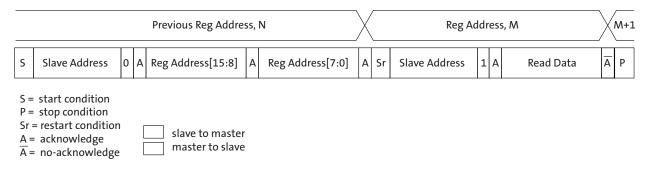

## Sequential READ, Start From Random Location

This sequence (Figure 20) starts in the same way as the single READ from random location (Figure 18). Instead of generating a no-acknowledge bit after the first byte of data has been transferred, the master generates an acknowledge bit and continues to perform byte READs until "L" bytes have been read.

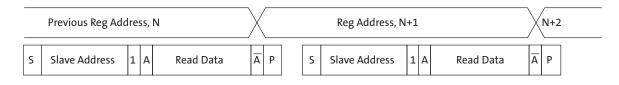

## Sequential READ, Start From Current Location

This sequence (Figure 21) starts in the same way as the single READ from current location (Figure 19 on page 25). Instead of generating a no-acknowledge bit after the first byte of data has been transferred, the master generates an acknowledge bit and continues to perform byte READs until "L" bytes have been read.

#### Figure 21: Sequential READ, Start From Current Location

## **Single WRITE to Random Location**

This sequence (Figure 22) begins with the master generating a start condition. The slave address/data direction byte signals a WRITE and is followed by the HIGH then LOW bytes of the register address that is to be written. The master follows this with the byte of write data. The WRITE is terminated by the master generating a stop condition.

## Figure 22: Single WRITE to Random Location

# Sequential WRITE, Start at Random Location

This sequence (Figure 23) starts in the same way as the single WRITE to random location (Figure 22 on page 26). Instead of generating a no-acknowledge bit after the first byte of data has been transferred, the master generates an acknowledge bit and continues to perform byte WRITEs until "L" bytes have been written. The WRITE is terminated by the master generating a stop condition.

#### Figure 23: Sequential WRITE, Start at Random Location

# **Programming Restrictions**

The following sections list programming rules that must be adhered to for correct operation of the MT9F002. Refer to the MT9F002 Register Reference document for register programming details.

#### Table 6:Definitions for Programming Rules

| Name  | Definition                                                                                                                                                                                 |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| xskip | xskip = 1 if x_odd_inc = 1; xskip = 2 if x_odd_inc = 3; xskip = 4 if x_odd_inc = 7                                                                                                         |

| yskip | <pre>yskip = 1 if y_odd_inc = 1; yskip = 2 if y_odd_inc = 3; yskip = 4 if y_odd_inc = 7;<br/>yskip = 8 if y_odd_inc = 15; yskip = 16 if y_odd_inc = 31; yskip = 32 if y_odd_inc = 63</pre> |

#### **X Address Restrictions**

The minimum column address available for the sensor is 24. The maximum value is 4647.

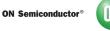

#### Effect of Scaler on Legal Range of Output Sizes

When the scaler is enabled, it is necessary to adjust the values of x\_output\_size and y\_output\_size to match the image size generated by the scaler. The MT9F002 will operate incorrectly if the x\_output\_size and y\_output\_size are significantly larger than the output image. To understand the reason for this, consider the situation where the sensor is operating at full resolution and the scaler is enabled with a scaling factor of 32 (half the number of pixels in each direction). This situation is shown in Figure 24.

#### Figure 24: Effect of Limiter on the Data Path